OVERVIEW

저유전상수 박막

저유전상수 박막(Low-k)

반도체산업

반도체산업은 지금까지 무한한 가능성을 가진 최첨단 산업으로서 끊임없이 발전해 왔으며 그것은 반도체소자의 고집적화를 통한 logic chip set 의 속도향상과 메모리 chip의

고밀도화에 의한 기억용량 증대에 의해 이루어졌다. 우리나라의 경우 메모리 반도체 제조기술은 삼성전자, 하이닉스 반도체가 세계적으로 60%에 달하는 점유율을 보유할 정도로

발전해 있으나 전체 반도체 시장의 75%를 차지하는 연산처리 장치(MPU), system-on-chip(SoC)와 같은 비메모리 소자의 경우 1% 정도의 점유율에 그치며 아직도 많은 노력이

필요한 실정이다.

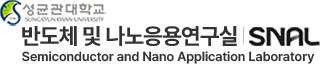

최근 세계적인 반도체 회사들이 초점을 맞추어 개발하고 있는 logic chip 속도는 수 GHz, 메모리 용량은 수 GB 수준에 달하고 있으며 이를 실현 하기 위해서 반도체소자 제작시

9층 이상의 다층배선구조와 100 nm 이하의 배선간격이 필요하게 되었다. 지금까지 일반적인 chip의 속도는 트랜지스터의 스위칭 속도에 크게 좌우되었으나 고집적 고밀도의

chip 속도는 스위칭 속도보다 배선에 의한 RC delay(R은 금속배선의 저항, C 는 금속배선 사이 유전체의 커패시턴스)에 의해 결정된다. Chip의 고집적, 고밀도화를 위해

배선간격이 특정수준 이하로 줄어들면 배선 사이의 cross-talk noise와 RC delay에 의한 방해로 소자의 스위칭 속도는 오히려 감소한다.

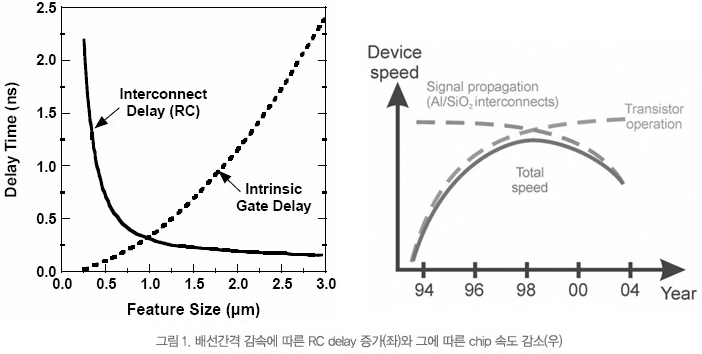

RC delay를 감소시키기 위해서는 층간절연막의 유전율의 감소나 금속배선의 저항의 감소가 필수적이다. 이러한 이유로 전기전도도가 큰 구리를 배선금속으로 하여 이와 함께 저유전체를 활용하는 Cu/low-k integration이 현재 반도체소자 개발에서 가장 핵심적으로 연구되고 있는 항목 중 하나이다. 구리배선은 기존에 쓰이던 알루미늄 배선보다 전기전도도가 우수함에도 불구하고 기체화되기 어려워 반도체 공정에 사용하는 진공 증착 및 건식에칭에 적용할 수 없는 한계가 있었으나 전기도금 기술과 식각공정을 피할 수 있는 dual damascene에 의한 배선공정이 가능해져 130 nm 공정세대부터 logic LSI에서 알루미늄을 대신하게 되었다.

그림 2와 같이 현재 양산되고 있는 90 nm급 logic 소자에는 back end of line(BEOL)에서도 AI/SiO₂ 대신 Cu/low-k 재료를 적용하고 있다.

반도체공정에서 일반적으로 사용되는 CVD SiO₂ 박막의 k 값은 보통 4.0 수준을 나타내며 이러한 k 값을 3.0 정도로만 낮추어도 delay는 25% 정도가 감소하는 것으로 알려져 왔다.

따라서, Cu/저유전 절연막을 통해 현재까지 초고속 반도체소자 제작이 가능하였으며 현재 국외 국내 유수 의 반도체회사들의 차세대 배선기술 개발은 모두 Cu/low-k 재료에 초점이

맞추어져 진행되고 있다. Cu 배선공정이 고집적화 됨에 따라 유전상수가 더 낮은 새로운 low-k 재료가 필요하기 때문에 새로운 물질의 개발이 요구된다.